컴퓨터의 구조는 내부 레지스터, 타이밍과 제어구조 명령어 집합에 의해 정의

레지스터 전송 언어

레지스터(Register)에 저장된 데이터의 조작을 위해 실행되는 동작을 마이크로연산(micro-operation)이라 한다.

이는 하나의 클럭 펄스 내에서 실행되는 기본적인 동작(ex shift, count clear, load…)

디지털 컴퓨터의 구조를 정의하기 위해서 논의 되어야 할 내용

레지스터의 종류와 그 기능

레지스터에 저장된 이진 정보를 가지고 수행되는 일련의 마이크로 연산들

일련의 마이크로 동작을 온/오프 시킬 수 있는 제어기능

레지스터 전송

P:R_2<-R_1: if(P=1) then (R_2 <- R_1), source register로 부터 target register로의 연결과

조건부 처리가 가능할 수 있도록 병렬 로드 기능이 있어야 한다.

레지스터 전송을 나타내는 각 문장들은 그 전송을 수행하는 하드웨어가 구성되어 있음을 의미한다.

레지스터의 구조 및 비트 표현 Assembly Language 참고

CPU(central processing unit) design

CPU 내의 다양한 디바이스들간 상호 연결

- 직접 연결: 연결 복잡도가 장치수의 제곱에 비례 n(n-1)/2

- 버스 연결: 공용선에 의해 연결

가장 가성비 높은 연결 방식

관리를 위한 다양한 방법이 제시된다.

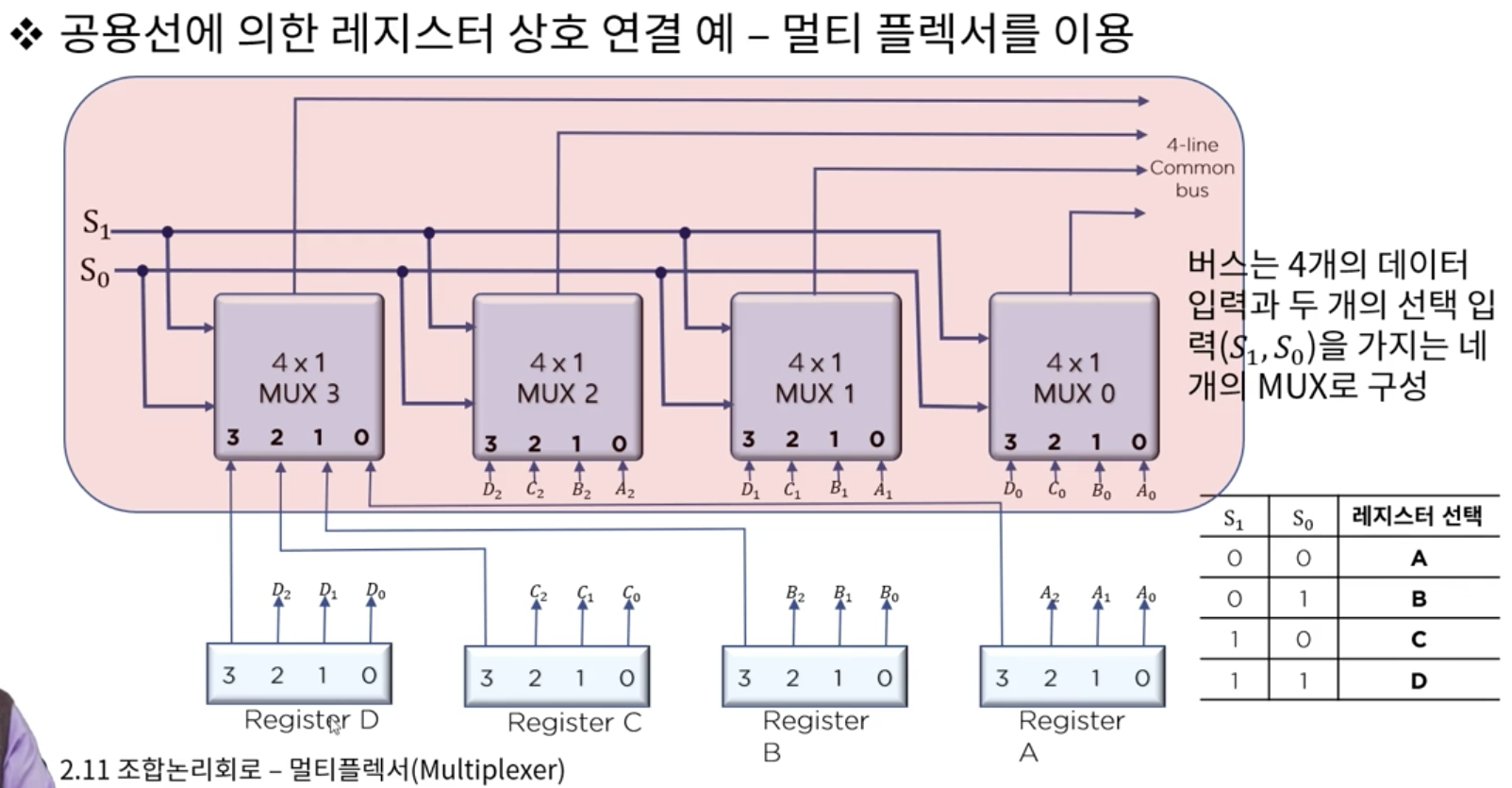

멀티플렉서를 이용해서 공용선 구현

멀티플렉서를 이용해서 공용선 구현버스는 4개의 데이터 입력과 두 개의 선택 입력(s_1, s_0)을 가지는 네개의 MUX로 구성(위 그림)

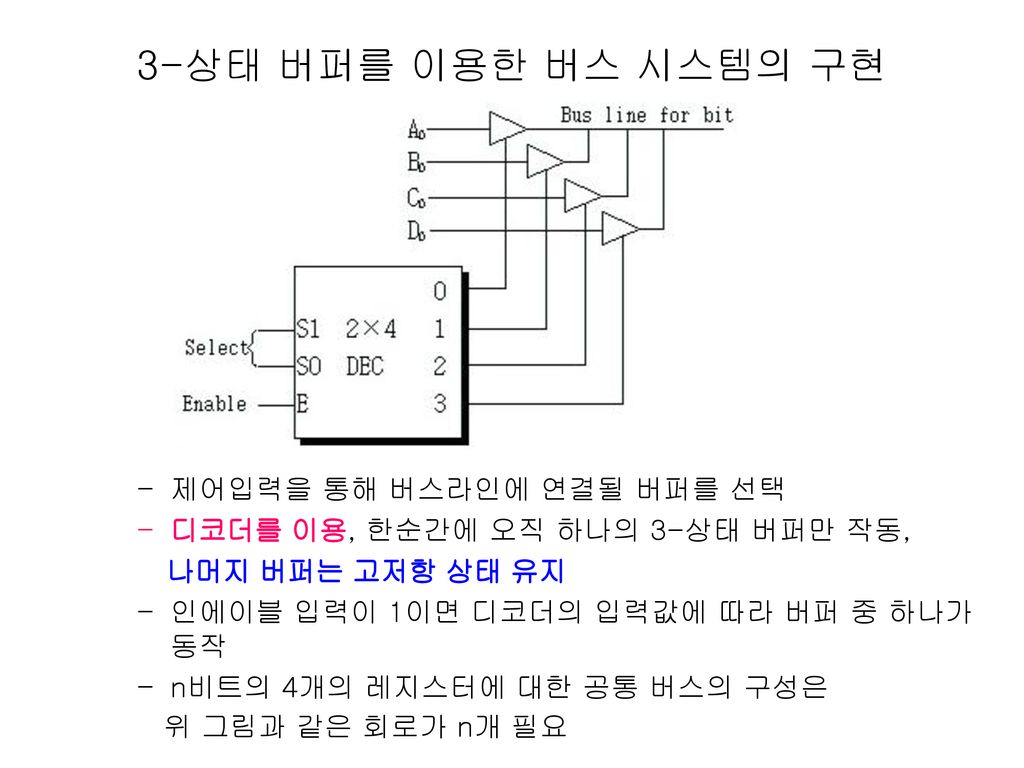

3-상태 버스를 이용한 버스 버퍼

3-상태 버스를 이용한 버스 버퍼스택(Stack): 자료의 입력과 출력을 한 곳(방향)으로 제한한 저장구조(LILO)

큐(Queue): 입력과 출력이 각기 서로 다른 부분에서 진행 front, rear(FIFO)

데크(Deque): 스택과 큐의 동작을 동시에 가능하도록 디자인된 자료구조